- Vhdl Code For Serial Adder Using Finite State Machine

- Vhdl Code For Serial Adder Using Finite State Machine Programming

- 4 Bit Serial Adder

- Vhdl Code For Serial Adder Using Finite State Machine Learning

Vhdl Code For Serial Adder Using Finite State Machine

Vhdl Code For Serial Adder Using Finite State Machine Equilibrium Unemployment Theory Pissarides Pdf Electric Rain Swift 3d 6.0.933 Python Event Driven Serial Gokusen S2 Sub Indo Consent Form Pm 330 Pdf Cm 03/04 Patch Update Ultramega Ok Zip Download Ennum Ninakkai Padam Mp3 Downlod Pusha TExodus Mp3. Introduction¶ In previous chapters, we saw various examples of the combinational circuits. Using the FSM VHDL code template provided above, you will implement a Finite State Machine in its canonical implementation. Moreover, you should be able to implement you own Vending Machine in VHDL! If you appreciated this post, please help us to share it with your friend.

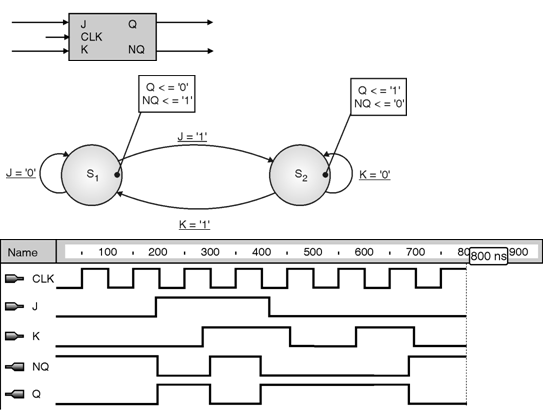

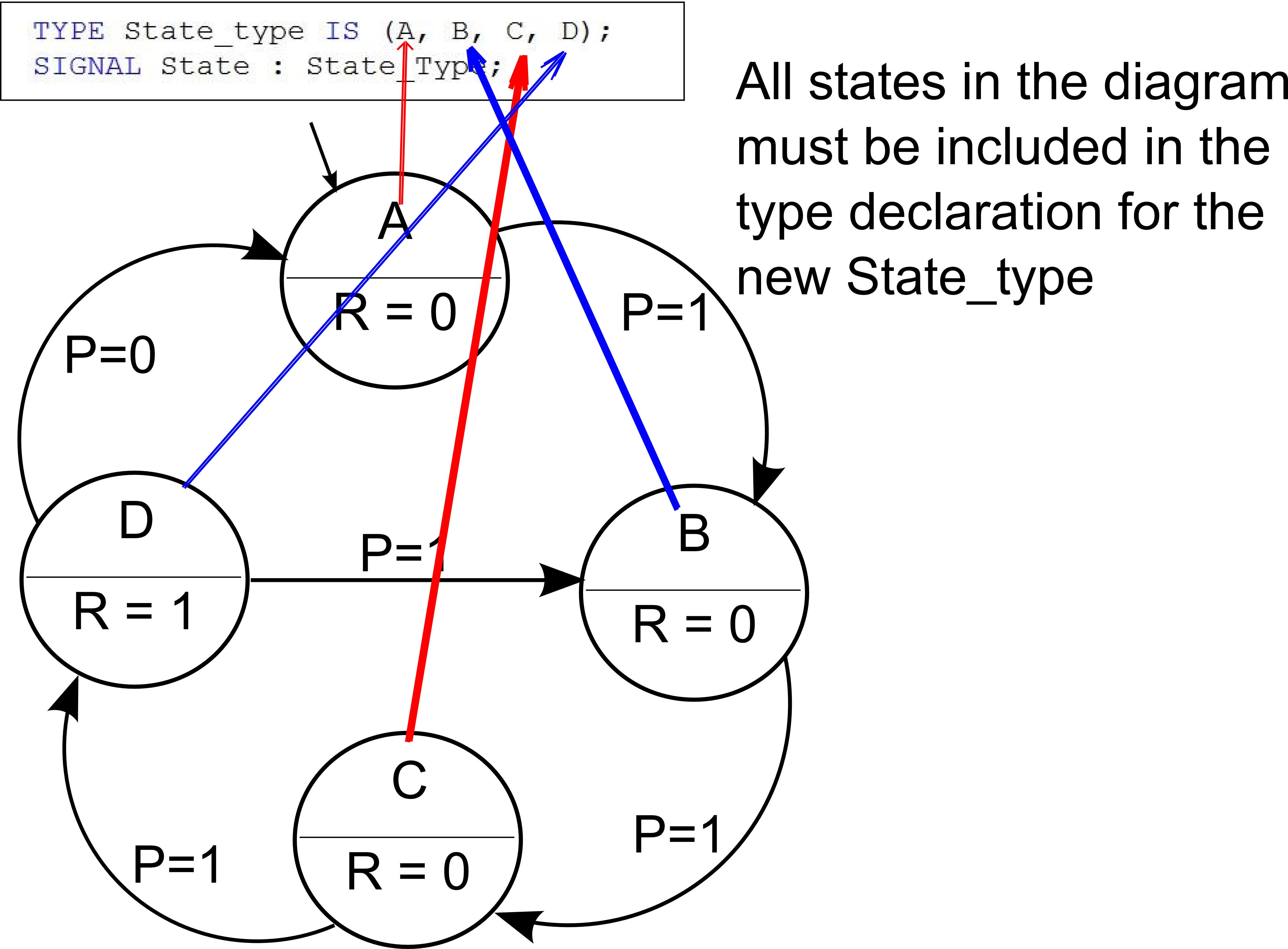

A state machine is a sequential circuit that advances through a number of states. To describe a state machine in Quartus II VHDL, you can declare an enumeration type for the states, and use a Process Statement for the state register and the next-state logic.

Binary adder and subtractor spartan 3 1, vhdl code for serial adder using moore type fsm serial adder verilog 4 bit serial adder when doing digital system design it is very common to begin by defining how the system works with a finite state. Aug 25, 2018 A finite-state machine (FSM) is a mechanism whose output is dependent not only on the current state of the input, but also on past input and output values. Whenever you need to create some sort of time-dependent algorithm in VHDL, or if you are faced with the problem of implementing a computer program in an FPGA, it can usually be solved.

The VHDL example shown below implements a 3-state state machine.

This state machine includes a Process Statement that is activated on every positive edge of the clk control signal for the next-state logic, and a Process Statement that is activated on a change in the state variable. This state machine has an asynchronous reset, which the Compiler recognizes.

Note: The Compiler also recognizes state machines with a synchronous reset. |

The signal state stores the current state of the state machine. The declaration of the type STATE_TYPE defines the states s0, s1, and s2 for state_machine.

At startup, the state machine is initialized to the reset state. If there is no reset state, the state machine is initialized to the first state in the Type Declaration. Otherwise, the first Case Statement determines the transitions between the states (that is, which state to enter on the next rising edge of clk) and the second Case Statement determines the value of the outputs for each state.

The Compiler recognizes state machines and reports them as such in the State Machines section of the Report window only if all of the following conditions are met:

The type of the signal or variable that represents the state machine must be an enumerated type.

The Process Statement that describes the state machine must be clocked, and must contain an If Statement that checks for a positive edge of the

clkcontrol signal.The state machine behavior, that is, the next-state logic, is defined with Case Statements at the top level.

All assignments to the signal or variable that represents the state machine are within the process.

The state machine must have more than two states.

VHDL state machines that do not meet these conditions are converted into logic gates and registers that are not listed as state machines in the Report window. The Compiler also converts VHDL state machines to 'regular' logic when the ENUM_ENCODING attribute is used to manually specify state assignments in a project.

Note: Because the Compiler usually produces the best results, Altera recommends that you do not use the |

You can assign states in the following ways:

Vhdl Code For Serial Adder Using Finite State Machine Programming

4 Bit Serial Adder

For more information, refer to the following sections of the IEEE Std 1076-1993 IEEE Standard VHDL Language Reference Manual:

Vhdl Code For Serial Adder Using Finite State Machine Learning

Section 8.1: Wait Statement

Section 8.6: If Statement

Section 8.7: Case Statement

Section 9.2: Process Statement